Slot 1 can be programmed with other slots in the same channel.

In other words, slot 2 can be programmed into the same FIFO as slot 1 but not other slots.

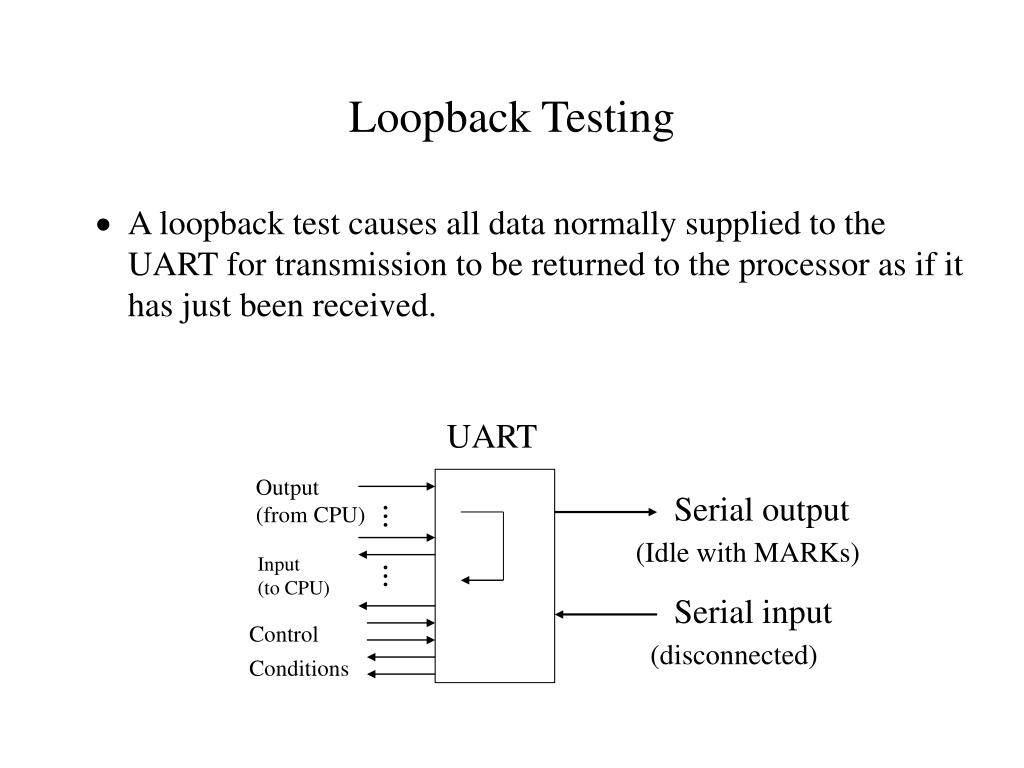

AUDIO LOOPBACK TESTING PLUS

The LowPower Mode bit in the AACIMAINCR register must be set only after the CODEC has been programmed to go to low-power mode, plus the time it takes for AACIBITCLK and AACISDATAIN to go LOW (normally the TS2_PDOWN parameter in the CODEC datasheets).The MainRxBusy bit of the AACIMAINFR register and the TxBusy bits of the AACISR1-4 registers must be polled for zero before programming the CODEC into low-power mode. All the receive logic and the FIFO transmit logic must be disabled and not busy before low-power mode is entered.The AC-Link can be programmed into low-power mode only through the Slot Tx registers and not through the channels.The Slot Tx/Rx register enables (Sl1T圎n, Sl2T圎n, Sl12T圎n, Sl1R圎n, Sl2R圎n, Sl12R圎n bits in the AACIMAINCR register) must not be disabled while the corresponding Slot Tx/Rx busy bit of that register (Sl1TxBusy, Sl2TxBusy, Sl12TxBusy, Sl1RxBusy, Sl2RxBusy, Sl12RxBusy bits in the AACISLFR register) is HIGH.The FIFOs must not be disabled in compact mode.For example, if slots 4 and 5 are to be stored in a FIFO, slot 4 must be the first data into the FIFO and slot 5 the second. Data must be stored in the Tx FIFO lower slot first.

All slots programmed to be transmitted from, or received by a given channel must have the same sample rate.Similarly, when the receive FIFO of a channel is in compact mode, the RSize bits in the corresponding AACIRXCR1-4 register must indicate only a 12-bit, or 16-bit data width. When the Transmit FIFO of a channel is in compact mode, the TSize bits in the corresponding AACITXCR1-4 register must indicate only a 12-bit, or 16-bit data width.The ForcedSYNC bit must not be set to 1 when the AACI is in normal mode. The ForcedSYNC bit of the AACISYNC register must be kept asserted HIGH for at least 1.3µs in low-power mode in order to restart the AC-Link with a warm reset.The ForcedRESET bit of the AACIRESET register is asserted LOW for at least 1µs in low-power mode in order to restart the AC-Link with a cold reset.Similarly, you must not program more than one channel to receive data for a slot at a time. You do not program more than one channel to transmit data for a slot at a time.This takes two cycles of AACIBITCLK and two cycles of PCLK, and that is approximately 182ns at 100MHz PCLK. Once a value has been written into a AACITXCR1-4 register, the AACI ignores further writes to the same register until the data from the previous write is synchronized to the AACIBITCLK domain.The AACITXCR1-4 and AACIRXCR1-4 registers are not programmed for more than eight slots per channel at a time.

AUDIO LOOPBACK TESTING SOFTWARE

Software must poll for the TxBusy and RxBusy bits in the AACISR1-4 to be cleared before writing into the AACIRXCR1-4 and AACITXCR1-4 registers.

0 kommentar(er)

0 kommentar(er)